## TNETX3270 ThunderSWITCH™ 24/3 ETHERNET™ SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B - NOVEMBER 1997 - REVISED APRIL 1999

- Port Configurations:

- Twenty-Four 10-Mbit/s Ports

- Ports Arranged in Three Groups of Eight Ports in a Multiplexed Interface

- Direct Multiplexer Interface to TNETE2008

- Full and Half Duplex

- Half-Duplex Collision-Based Flow Control

- Full-Duplex IEEE Std 802.3x Flow Control

- Interoperable Support for IEEE Std 802.1Q VLAN

- Speed, Duplex, and Pause Autonegotiation With Physical Layer (PHY)

- Three 10-/100-Mbit/s Ports

- Direct Interface to TNETE2101

- Full and Half Duplex

- Half-Duplex Collision-Based Flow Control

- Full-Duplex IEEE Std 802.3x Flow Control

- Interoperable Support for IEEE Std 802.1Q VLAN

- Pretagging Support

- Port Trunking and Load Sharing

- LED Indication of Port Status

- SDRAM Interface

- Direct Interface to 8-Bit/Word and 16-Bit/Word, 16-Mbit, and 64-Mbit SDRAMs

- 32-Bit-Wide Data Bus

- Up to 32 Mbytes Supported

- 83.33-MHz SDRAM Clock

- 12-ns (-12) SDRAMs Required

- Remote Monitoring (RMON) Support Groups 1, 2, 3, and 9

- Direct I/O (DIO) Management Interface

Eight Bits Wide

- CPU Access to Statistics, Registers, and Management Information Bases (MIBs)

- Internal Network Management Port

- Forwards Spanning-Tree Packets to CPU

- Serial Media-Independent Interface (MII) for PHY Control

- EEPROM Interface for Autoconfiguration (No CPU Required for Nonmanaged Switch)

- Internal Address-Lookup/Frame-Routing Engine

- Interoperable Support for IEEE Std 802.1Q VLAN

- Supports IEEE Std 802.1D Spanning Tree

- Thirty-Two Assignable Virtual LANs (VLANs)

- Multiple Forwarding Modes

- 2K Total Addresses Supported

- Port Mirroring

- IEEE Std 1149.1 (JTAG) Interface (3.3-V Signals)

- 2.5-V Process With 3.3-V-Drive I/O

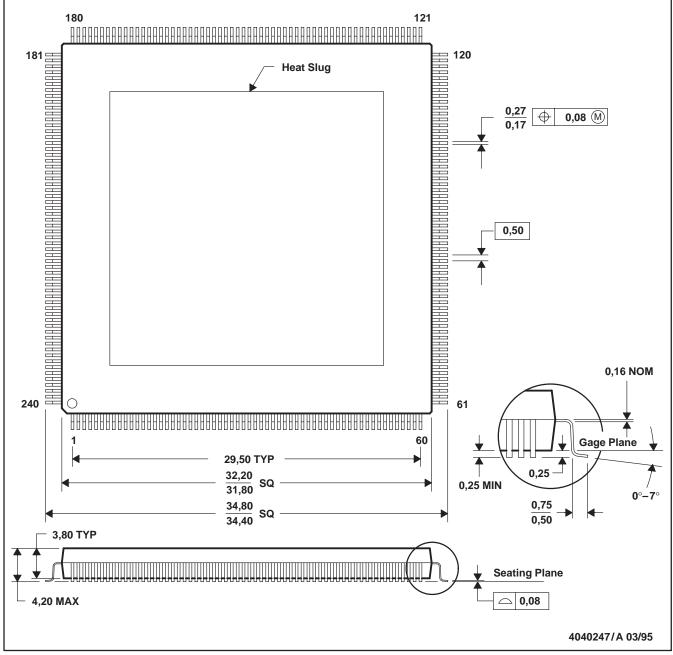

- Packaged in 240-Terminal Plastic Quad Flatpack

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI and ThunderSWITCH are trademarks of Texas Instruments Incorporated.

Ethernet is a trademark of Xerox Corporation.

Secure Fast Switching is a trademark of Cabletron Systems, Inc.

Port-trunking and load-sharing algorithms were contributed by Cabletron Systems, Inc. and are derived from, and compatible with, Secure Fast Switching™.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999, Texas Instruments Incorporated

1

# **TNETX3270** ThunderSWITCH<sup>™</sup> 24/3 ETHERNET<sup>™</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B - NOVEMBER 1997 - REVISED APRIL 1999

#### description

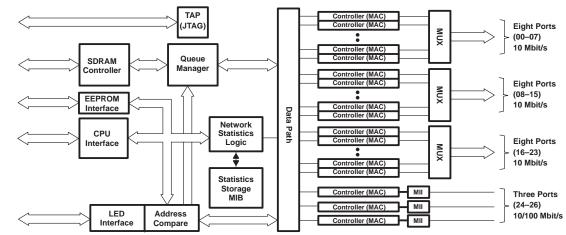

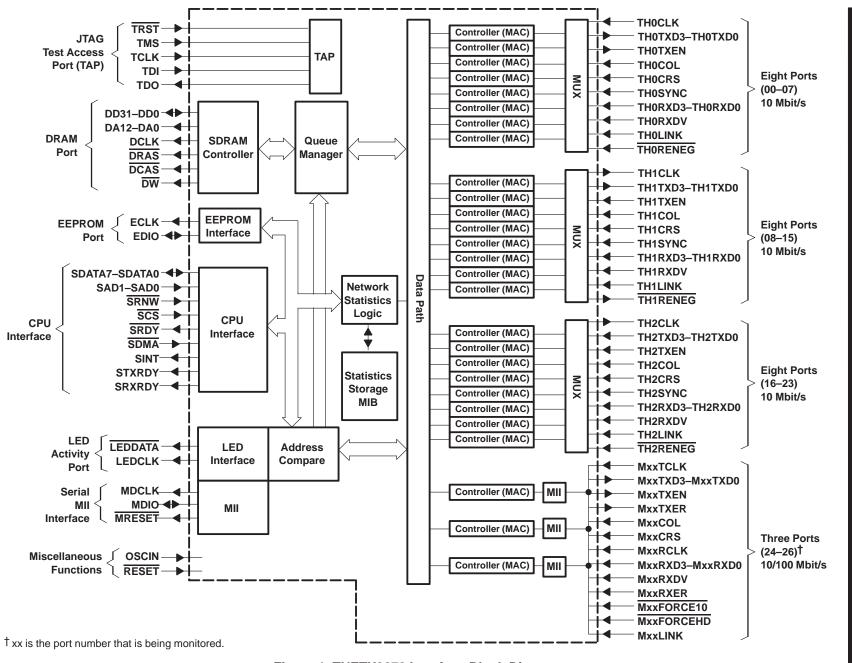

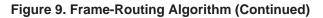

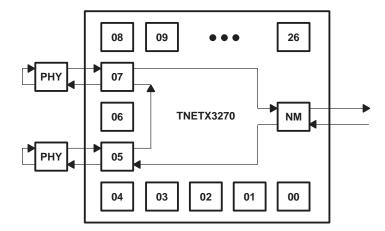

The TNETX3270 provides highly integrated switching solutions that allow network designers to lower overall system costs. Based on Texas Instruments (TI™) ThunderSWITCH™ architecture, the TNETX3270 design integrates 24 full-duplex 10-Mbit/s ports and 3 full-duplex 10-/100-Mbit/s ports, as well as an address-lookup engine, all in a single 240-pin package. All ports on the TNETX3270 are designed to support multiple addresses, cut-through or store-and-forward modes of operation, and VLAN. The 10-/100-Mbit/s ports have media-independent interface (MII)-compatible interfaces and can be configured to work as MII uplinks to high-speed switching fabrics. All three of the 10-/100-Mbit/s ports can be logically combined into a single high-performance uplink channel that can be used to provide up to 600-Mbit/s switch-to-switch connections.

The TNETX3270 incorporates an internal content-addressable memory (CAM) capable of supporting 2,048 end stations from a single switch. In addition, the device supports 32 user-configurable VLAN-broadcast domains (IEEE Std 802.1Q), which allows IEEE Std 802.1P priority support interoperability, IEEE Std 802.3X full-duplex flow control, and a collision-based flow-control scheme. The TNETX3270 also integrates an EEPROM interface that allows the device to be initialized and configured without the added expense of a CPU. All of these features on chip greatly reduce the number of external components required to build a switch.

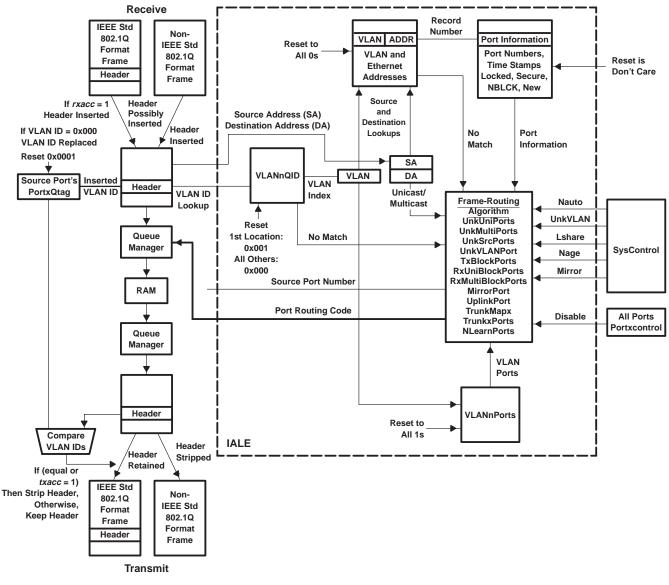

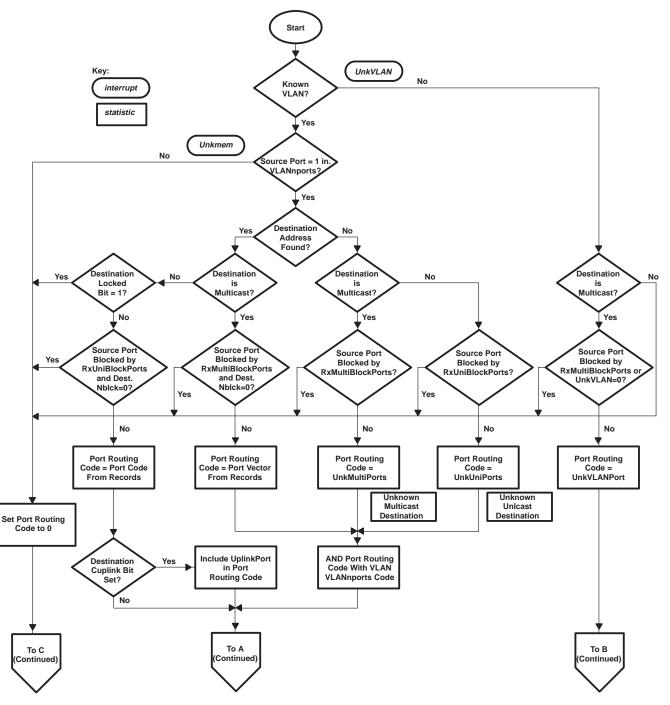

The internal address-lookup engine (IALE) supports up to 2K unicast/multicast and broadcast addresses and up to 32 IEEE Std 802.1Q VLANs. For interoperability, each port can be programmed as an access port or non-access port to recognize VLAN tags and transmit frames with VLAN tags to other systems that support VLAN tagging. The IALE performs destination- and source-address comparisons and forwards unknown source- and destination-address packets to ports specified via programmable masks.

# **TNETX3270** ThunderSWITCH<sup>TM</sup> 24/3 ETHERNET<sup>TM</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

#### Contents

| Giant (Long) Frames<br>Short Frames<br>Receive Filtering of Frames<br>Data Transmission<br>Transmit Control<br>Adaptive Performance Optimization<br>(APO) (Transmit Pacing)<br>Interframe Gap Enforcement<br>Backoff<br>Receive Versus Transmit Priority<br>Uplink Pretagging<br>EEPROM Interface<br>Interaction of EEPROM Load With the SIO Register<br>Summary of EEPROM Load Outcomes<br>Compatibility With Future Device Revisions | <b>4 5 6 13 18 18 18 19 22 22 22 22 22 23 23 23</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                  |

| HIGHZ instruction                                                                                                                                                                                                                                                                                                                                                                                                                      | 29<br>29                                            |

| Lamp Test                                                                                                                                                                                                                                                                                                                                                                                                                              | 30                                                  |

| Multi-LED Display                                                                                                                                                                                                                                                                                                                                                                                                                      | 30                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>30</b><br>30                                     |

| 10-Mbit/s MAC Interfaces (Ports 00–23)<br>10-/100-Mbit/s MAC Interfaces (Ports 24–26)                                                                                                                                                                                                                                                                                                                                                  | 30<br>34                                            |

| 10-/100-Mbit/s Port Configuration                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

| 10-/100-Mbit/s Port Configuration                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

| in a Nonmanaged Switch                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                  |

| 10-/100-Mbit/s Port Configuration                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

| in a Managed Switch                                                                                                                                                                                                                                                                                                                                                                                                                    | 36                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

| SDRAM Interface                        |

|----------------------------------------|

| SDRAM-Type and Quantity Indication     |

| Initialization                         |

| Refresh                                |

| Frame Routing                          |

| VLAN Support                           |

| IEEE Std 802.1Q Headers – Reception    |

| IEEE Std 802.1Q Headers – Transmission |

| Address Maintenance 40                 |

| Spanning-Tree Support 41               |

| Aging Algorithms                       |

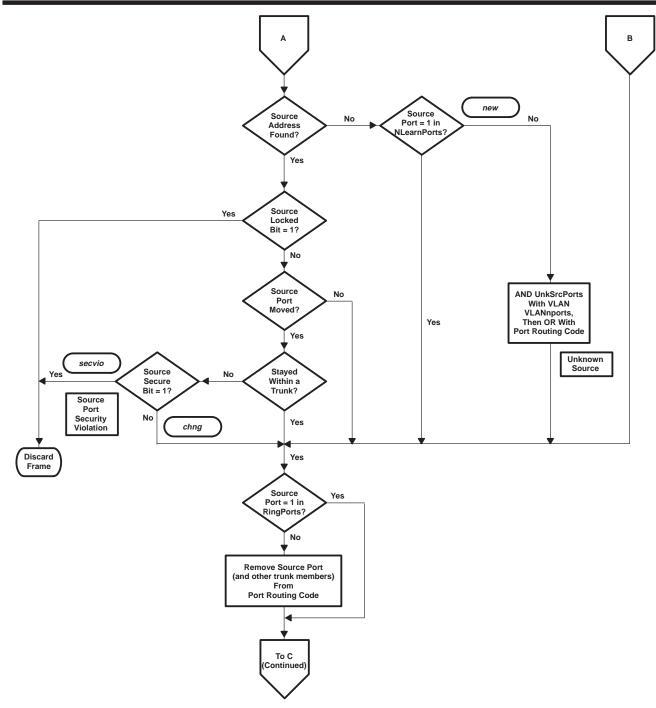

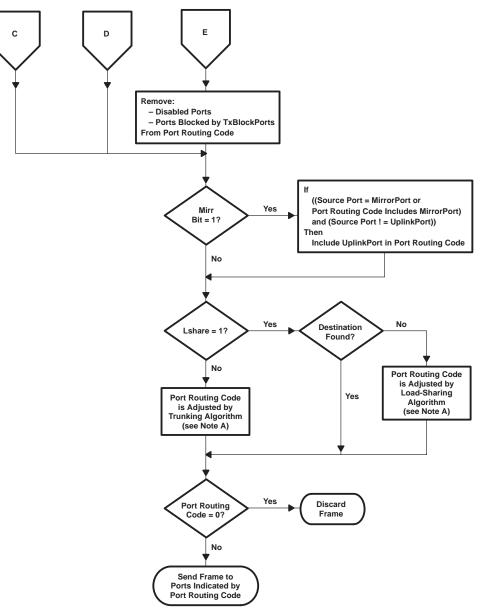

| Frame-Routing Determination            |

| Port Mirroring                         |

| Port Trunking/Load Sharing             |

| Flow Control                           |

| Collision-Based Flow Control 46        |

| IEEE Std 802.3 Flow Control 46         |

| Internal Wrap Test 48                  |

| Duplex Wrap Test 49                    |

| Port Mirroring 50                      |

| Copy to Uplink 50                      |

| Absolute Maximum Ratings51             |

| Recommended Operating Conditions       |

| Electrical Characteristics51           |

| Parameter Measurement Information      |

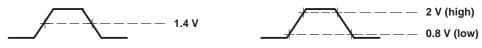

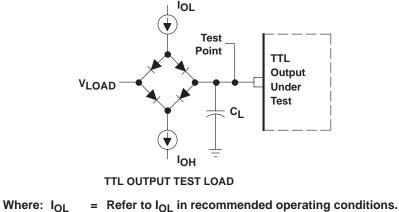

| Test Measurement 52                    |

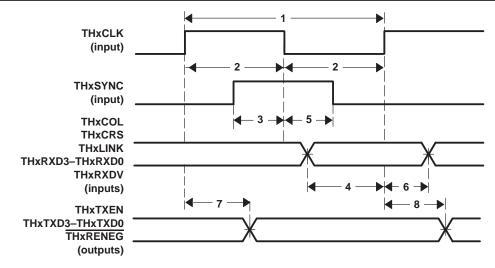

| 10-Mbit/s Interface (Ports 00–23) 53   |

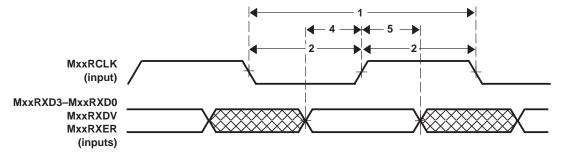

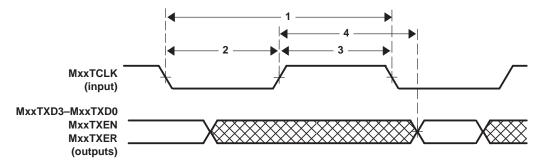

| 10-/100-Mbit/s MAC Interface54         |

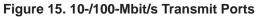

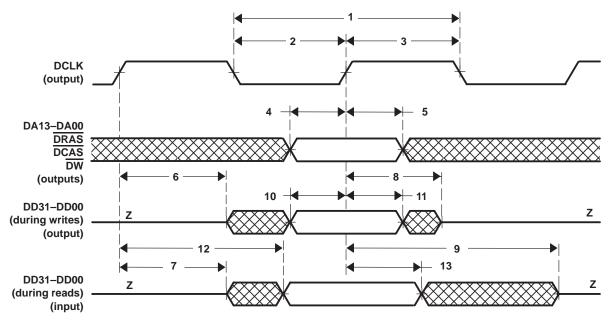

| SDRAM Interface56                      |

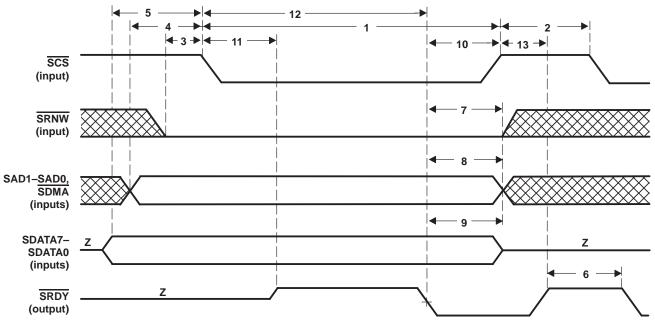

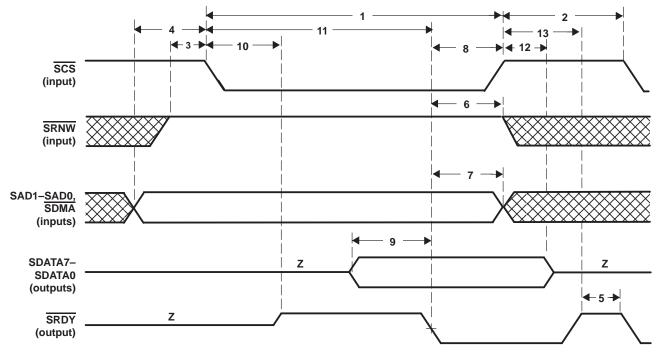

| DIO/DMA Interface 58                   |

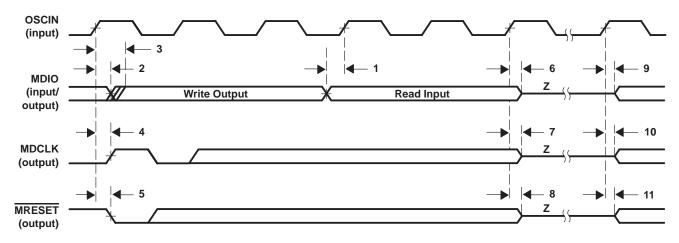

| Serial MII Management Interface60      |

| EEPROM Interface 61                    |

| LED Interface                          |

| Power-Up OSCIN and RESET63             |

| Mechanical Data                        |

## TNETX3270 ThunderSWITCH<sup>TM</sup> 24/3 ETHERNET<sup>TM</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

**PGV PACKAGE** (TOP VIEW) V 00/2.5/ V 00/2.5/ 00/21 00/21 00/16 00/16 00/16 00/16 00/16 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/12 00/1 GND SDATA1 SDATA0 SRNW VDD(2.5V) SDMA V DD(3.3V) MDCLK SDATA3 SDATA2 DD25 DD24 Π 181 182 183 DD26 E 120 DD27 119 118 110 117 116 115 114 113 184 185 186 V<sub>DD(2.5V)</sub> DD29 DD30 187 188 189 DD31 GND DCAS DRAS 112 111 109 108 107 106 190 191 DW V<sub>DD(3.3V)</sub> DCLK 192 193 GND DA00 DA01 194 195 VDD(2.5V) M26FORCE10 M26FORCEHD M26FORCEHD M26LINK 196 197 198 199 V<sub>DD(2.5V)</sub> DA02 DA03 200 201 202 M26RXER M26RXER GND M26RXDV DA04 GND DA05 202 203 204 205 206 M26RXD3 DA06 DA07 M26RXD1 DA09 M26RXD0 DA10 \_\_\_\_\_ GND \_\_\_\_\_ DA11 \_\_\_\_ 200 207 208 209 GND M26RCLK M26CRS DA12 210 211 212 213 214 215 □ V<sub>DD(2.5V)</sub> □ M26COL V<sub>DD(2.5V)</sub> M26TXER THORENEG GND M26TXEN **—** M26TXD3 M26TXD2 M26TXD2 M26TXD1 TH0TXD1 216 217 218 219 220 221 222 THOTXD2 M26TXD0 M26TCLK M26TCLK GND M25FORCE10 THOTXEN M25FORCEHD M25FORCEHD M25LINK THOCLK 223 224 225 THOCOL E VDD(2.5V) M25RXER M25RXDV GND V<sub>DD(2.5V)</sub> THORXDV 225 226 227 228 229 230 231 THORXDO THORXD1 M25RXD3 V<sub>DD(3.3V)</sub> TH0RXD2 □ V<sub>DD(3.3V)</sub> □ M25RXD2 M25RXD2 M25RXD1 M25RXD0 GND THORXD3 THOI INK 232 233 234 235 236 237 238 TH1RENEG GND M25RCLK M25CRS M25COL VDD(2.5V) M25TXER M25TXER M25TXER GND TH1TXD1 V<sub>DD(2.5V)</sub> 230 240( TH1TXEN C M25TXD3 ΗH U ШЦ L Ш TH1SYNC TH1SYNC TH1CLK TH1CLK TH1CLK TH1CLK TH1CLK TH1CLK TH1CLK TH1RXDV GND GND GND TH1RXDY TH1RXDY TH1RXDY TH1RXDY TH1RXDZ TH1RXDZ TH1RXDZ TH1RXDZ TH1RXDZ TH1RXDZ TH2CKD TH2CCCD TH2CKD TH2C

ThunderSWITCH<sup>™</sup>24/3 WITH 24 10-MBIT/S PORTS AND 3

ETHERNET<sup>TM</sup> SWITCH 10-/100-MBIT/S PORTS VEMBER 1997 - REVISED APRIL 1999

**TNETX3270**

Figure 1. TNETX3270 Interface Block Diagram

## **TNETX3270** ThunderSWITCH<sup>™</sup> 24/3 ETHERNET<sup>™</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B - NOVEMBER 1997 - REVISED APRIL 1999

## **Terminal Functions**

# 10-Mbit/s MAC multiplexed interface (ports 00–23) is multiplexed into three groups (TH0, TH1, and TH2) of eight ports $^{\intercal}$

| TERMINAL                                                                                                                                               |                                                                              | 1/0 | INTERNAL              | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                   | NO.                                                                          |     | RESISTOR <sup>‡</sup> | DEGORFHON                                                                                                                                                                                                                                                                                                                             |

| TH0CLK<br>TH1CLK<br>TH2CLK                                                                                                                             | 222<br>2<br>23                                                               | I   | Pullup                | Interface clock. Eight ports are supported on each interface and use this common 20-MHz clock.                                                                                                                                                                                                                                        |

| TH0COL<br>TH1COL<br>TH2COL                                                                                                                             | 223<br>3<br>24                                                               | I   | Pulldown              | Interface collision sense. Assertion of THxCOL <sup>†</sup> during half-duplex operation indicates network collision on the current port. Additionally, during full-duplex operation, transmission of new frames does not start if this terminal is asserted.                                                                         |

| TH0CRS<br>TH1CRS<br>TH2CRS                                                                                                                             | 224<br>5<br>25                                                               | I   | Pulldown              | Interface carrier sense. THxCRS <sup>†</sup> indicates a frame carrier signal is being received on a current port.                                                                                                                                                                                                                    |

| THOLINK<br>TH1LINK<br>TH2LINK                                                                                                                          | 232<br>13<br>32                                                              | I   | Pulldown              | Interface link presence. THxLINK <sup>†</sup> indicates the presence of the connection on a port.<br>– Low = no link<br>– High = link good                                                                                                                                                                                            |

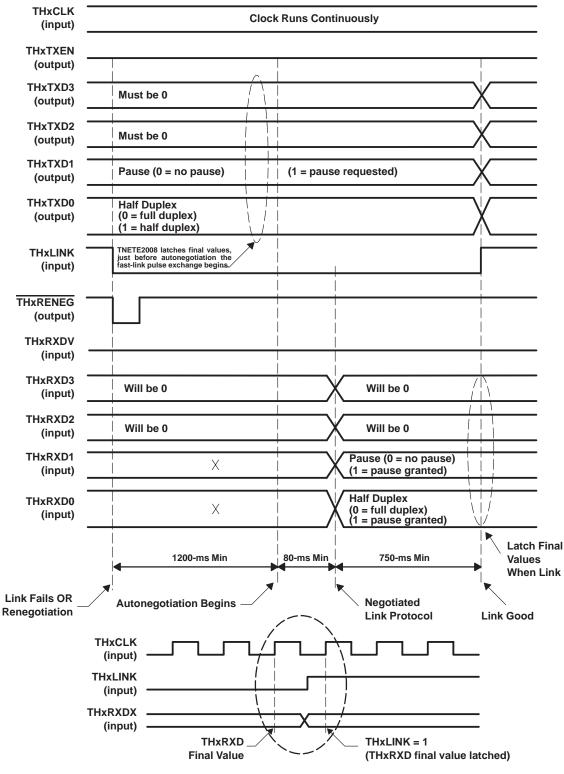

| THORENEG<br>TH1RENEG<br>TH2RENEG                                                                                                                       | 213<br>233<br>15                                                             | 0   | None                  | Interface renegotiate. A 1-0-1 sequence output on THxRENEG causes flow control and half/full <u>duplex for a</u> port to be renegotiated with its companion physical-layer (PHY) device. These THxRENEG terminals connect to IFFORCEHD on TNETE2008.                                                                                  |

| THORXD3<br>THORXD2<br>THORXD1<br>THORXD0<br>TH1RXD3<br>TH1RXD2<br>TH1RXD1<br>TH1RXD0<br>TH2RXD3<br>TH2RXD3<br>TH2RXD2<br>TH2RXD1<br>TH2RXD1<br>TH2RXD0 | 231<br>230<br>228<br>227<br>11<br>10<br>9<br>7<br>30<br>29<br>28<br>28<br>27 | I   | Pullup                | Interface receive data. The receive data nibble from the current port is synchronous to THxCLK. When the THxRXDV signal is 1, the receive data terminals contain valid information. THxRXD0 is the least significant bit and THxRXD3 is the most significant bit. These signals also are used to report the channel state to the MAC. |

| TH0TXEN<br>TH1TXEN<br>TH2TXEN                                                                                                                          | 219<br>240<br>21                                                             | 0   | None                  | Interface transmit enable. THxTXEN indicates valid transmit data on THxTXD.                                                                                                                                                                                                                                                           |

| TH0SYNC<br>TH1SYNC<br>TH2SYNC                                                                                                                          | 221<br>1<br>22                                                               | I   | Pullup                | Interface synchronize. THxSYNC is used to synchronize the port traffic between the media-access controller (MAC) and PHY. When THxSYNC is a 1, the current MAC-to-PHY path is the multiplexer interface TH0, and the PHY-to-MAC path is the multiplexer interface TH2. THxSYNC is sampled by the MAC on the falling edge of THxCLK.   |

$^{\dagger}$  THx = TH0, TH1, and TH2

‡ Internal resistors are provided to pull signals to known values. System designers should determine if additional pullups or pulldowns are required in their system.

# **TNETX3270** ThunderSWITCH™ 24/3 ETHERNET™ SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B - NOVEMBER 1997 - REVISED APRIL 1999

## **Terminal Functions (Continued)**

| TERMIN                                                                               | TERMINAL                                             |     | INTERNAL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------|------------------------------------------------------|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                 | NO.                                                  | 1/0 | RESISTOR | DESCRIPTION                                                                                                                                                                                                                                                                                                                                           |

| TH0TXD3<br>TH0TXD2<br>TH0TXD1<br>TH0TXD0<br>TH1TXD3<br>TH1TXD2<br>TH1TXD1<br>TH1TXD0 | 218<br>217<br>216<br>215<br>239<br>237<br>236<br>234 | ο   | None     | Interface transmit data. The transmit data nibble for the current port is synchronous to THxCLK. When THxTXEN is asserted, these signals carry data. THxTXD3–THxTXD0 are used during renegotiation to convey flow-control and duplex configuration requests to the PHY. THxTXD0 is the least significant bit and THxTXD3 is the most significant bit. |

| TH2TXD3<br>TH2TXD2<br>TH2TXD1<br>TH2TXD0                                             | 20<br>19<br>18<br>16                                 |     |          |                                                                                                                                                                                                                                                                                                                                                       |

| TH0RXDV<br>TH1RXDV<br>TH2RXDV                                                        | 226<br>6<br>26                                       | I   | Pulldown | Interface receive data valid. When THxRXDV is a 1, it indicates that the THxRXD lines contain valid data.                                                                                                                                                                                                                                             |

# 10-Mbit/s MAC multiplexed interface (ports 00–23) is multiplexed into three groups (TH0, TH1, and TH2) of eight ports<sup>†</sup> (continued)

THx = TH0, TH1, and TH2

## 10-/100-Mbit/s MAC interface (ports 24-26)<sup>‡</sup>

| TERMINAL                               |                 | 1/0  | INTERNAL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------|-----------------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                   | NO.             |      | RESISTOR |                                                                                                                                                                                                                                                                                                                                                                                 |

| M24COL<br>M25COL<br>M26COL             | 42<br>65<br>90  | I    | Pulldown | Collision sense. Assertion of MxxCOL in half-duplex signal indicates a network collision on that port. In full-duplex operation, transmission of new frames does not start if this terminal is asserted.                                                                                                                                                                        |

| M24CRS<br>M25CRS<br>M26CRS             | 43<br>66<br>92  | I    | Pulldown | Carrier sense. MxxCRS indicates a frame carrier signal is being received.                                                                                                                                                                                                                                                                                                       |

|                                        |                 |      |          | Speed selection (force 10 Mbit/s is active low)                                                                                                                                                                                                                                                                                                                                 |

| M24FORCE10<br>M25FORCE10<br>M26FORCE10 | 54<br>80<br>104 | I/O§ | Pullup   | – If pulled low by either the TNETX3270 or a PHY, the port operates at 10 Mbit/s.<br>– If not pulled low by either the TNETX3270 or a PHY, the internal pullup resistor holds<br>this signal high and the port operates at 100 Mbit/s. An external 4.7-kΩ pullup resistor<br>connected to V <sub>DD(3.3V)</sub> may be required, depending on the system layout.                |

| M24LINK                                | 52              |      |          | Connection status. MxxLINK indicates the presence of a port connection.                                                                                                                                                                                                                                                                                                         |

| M25LINK<br>M26LINK                     | 78<br>102       | I    | Pulldown | <ul> <li>If MxxLINK = 0, there is no link.</li> <li>If MxxLINK = 1, the link is good.</li> </ul>                                                                                                                                                                                                                                                                                |

|                                        |                 |      |          | Duplex selection (force half duplex is active low)                                                                                                                                                                                                                                                                                                                              |

| M24FORCEHD<br>M25FORCEHD<br>M26FORCEHD | 53<br>79<br>103 | I/O‡ | Pullup   | – If pulled low by either the TNETX3270 or the PHY, the port operates at half duplex.<br>– If not pulled low by either the TNETX3270 or the PHY, the internal pullup resistor holds<br>this signal high and the port operates at full duplex. An external 4.7-k $\Omega$ pullup resistor<br>connected to V <sub>DD(3.3V)</sub> may be required, depending on the system layout. |

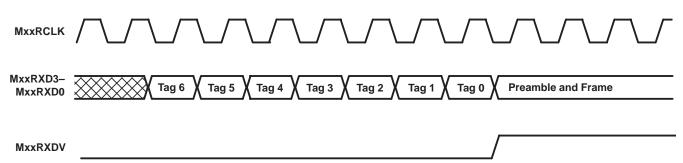

| M24RCLK<br>M25RCLK<br>M26RCLK          | 44<br>67<br>93  | I    | Pullup   | Receive clock. Receive clock source from the attached PHY or PMI device.                                                                                                                                                                                                                                                                                                        |

$\ddagger xx = ports 24, 25, and 26$

§ Not a true bidirectional terminal. It can only be actively pulled down (open drain).

## **TNETX3270** ThunderSWITCH<sup>™</sup> 24/3 ETHERNET<sup>™</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B - NOVEMBER 1997 - REVISED APRIL 1999

## **Terminal Functions (Continued)**

## 10-/100-Mbit/s MAC interface (ports 24-26) (continued)<sup>†</sup>

| TERMINAI                                 | -                    | 1/0 | 1/0      | 1/0                                                                                                                                                                                                                                                                                                                                     | 1/0 | INTERNAL | DESCRIPTION |

|------------------------------------------|----------------------|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------------|

| NAME                                     | NO.                  | 1/0 | RESISTOR | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |     |          |             |

| M24RXD3<br>M24RXD2<br>M24RXD1<br>M24RXD0 | 49<br>48<br>47<br>46 |     |          |                                                                                                                                                                                                                                                                                                                                         |     |          |             |

| M25RXD3<br>M25RXD2<br>M25RXD1<br>M25RXD0 | 73<br>71<br>70<br>69 | I   | Pullup   | Receive data (nibble receive data from the attached PHY or PMI device). Data on these signals is synchronous to MxxRCLK. MxxRXD0 is the least significant bit and MxxRXD3 is the most significant bit.                                                                                                                                  |     |          |             |

| M26RXD3<br>M26RXD2<br>M26RXD1<br>M26RXD0 | 98<br>97<br>96<br>95 |     |          |                                                                                                                                                                                                                                                                                                                                         |     |          |             |

| M24RXDV<br>M25RXDV<br>M26RXDV            | 50<br>75<br>99       | I   | Pulldown | Receive data valid. When high, MxxRXDV indicates valid data is present on the MxxRXD3–MxxRXD0 lines.                                                                                                                                                                                                                                    |     |          |             |

| M24RXER<br>M25RXER<br>M26RXER            | 51<br>76<br>101      | Ι   | Pulldown | Receive error. MxxRXER indicates a coding error on received data.                                                                                                                                                                                                                                                                       |     |          |             |

| M24TCLK<br>M25TCLK<br>M26TCLK            | 33<br>56<br>82       | I   | Pullup   | Transmit clock. Transmit clock source from the attached PHY or PMI device.                                                                                                                                                                                                                                                              |     |          |             |

| M24TXD3<br>M24TXD2<br>M24TXD1<br>M24TXD0 | 38<br>37<br>36<br>35 |     |          |                                                                                                                                                                                                                                                                                                                                         |     |          |             |

| M25TXD3<br>M25TXD2<br>M25TXD1<br>M25TXD0 | 61<br>60<br>59<br>57 | 0   | None     | Transmit data (nibble transmit data). When MxxTXEN is asserted, these signals carry transmit data. Data on these signals is synchronous to MxxTCLK. MxxTXD0 is the least significant bit and MxxTXD3 is the most significant bit.                                                                                                       |     |          |             |

| M26TXD3<br>M26TXD2<br>M26TXD1<br>M26TXD0 | 86<br>85<br>84<br>83 |     |          |                                                                                                                                                                                                                                                                                                                                         |     |          |             |

| M24TXEN<br>M25TXEN<br>M26TXEN            | 39<br>62<br>87       | 0   | None     | Transmit enable. MxxTXEN indicates valid transmit data on MxxTXD3–MxxTXD0.                                                                                                                                                                                                                                                              |     |          |             |

| M24TXER<br>M25TXER<br>M26TXER            | 41<br>63<br>89       | 0   | None     | Transmit error. MxxTXER allows coding errors to be propagated across the MII. MxxTXER is taken high when an under-run in the transmit FIFO for port xx occurs and causes fill data to be transmitted (MxxTXER is low otherwise). MxxTXER is asserted at the end of an under-running frame, enabling the device to force a coding error. |     |          |             |

<sup>†</sup> xx = ports 24, 25, and 26

# **TNETX3270** ThunderSWITCH<sup>TM</sup> 24/3 ETHERNET<sup>TM</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

## **Terminal Functions (Continued)**

## **SDRAM** interface

| TERMI                                                                                                                                                                                                                                                                                        | NAL                                                                                                                                                                                                                                                      |     | INTERNAL |                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                         | NO.                                                                                                                                                                                                                                                      | 1/0 | RESISTOR | DESCRIPTION                                                                                                                                                                                                                                                                        |

| DA13<br>DA12<br>DA11<br>DA10<br>DA09<br>DA08<br>DA07<br>DA06<br>DA05<br>DA04<br>DA03<br>DA02<br>DA01<br>DA00                                                                                                                                                                                 | 212<br>210<br>209<br>207<br>206<br>205<br>204<br>203<br>202<br>200<br>199<br>198<br>196<br>195                                                                                                                                                           | 0   | None     | SDRAM address bus (time-multiplexed bank, row, and column address). The address bus DA13–DA00 also provides the SDRAM mode register initialization value. DA13 is the most significant bit and DA00 is the least significant bit.                                                  |

| DCAS                                                                                                                                                                                                                                                                                         | 189                                                                                                                                                                                                                                                      | 0   | None     | SDRAM column address strobe. DCAS, in conjunction with DRAS and DW, determines the SDRAM commands.                                                                                                                                                                                 |

| DCLK                                                                                                                                                                                                                                                                                         | 193                                                                                                                                                                                                                                                      | 0   | None     | SDRAM clock (83.33-MHz clock to the SDRAMs). SDRAM commands, addresses, and data are sampled by the SDRAM on the rising edge of this clock.                                                                                                                                        |

| DD31<br>DD30<br>DD29<br>DD28<br>DD27<br>DD26<br>DD25<br>DD24<br>DD23<br>DD22<br>DD21<br>DD20<br>DD19<br>DD18<br>DD17<br>DD16<br>DD15<br>DD14<br>DD13<br>DD12<br>DD11<br>DD10<br>DD09<br>DD08<br>DD07<br>DD08<br>DD07<br>DD06<br>DD05<br>DD04<br>DD03<br>DD02<br>DD01<br>DD00<br>DD01<br>DD00 | 187<br>186<br>185<br>183<br>182<br>181<br>180<br>179<br>177<br>176<br>174<br>177<br>176<br>174<br>177<br>176<br>174<br>177<br>176<br>168<br>167<br>166<br>164<br>162<br>161<br>159<br>158<br>157<br>156<br>155<br>153<br>152<br>150<br>149<br>147<br>146 | I/O | Pullup   | SDRAM data bus (bidirectional bus used to carry SDRAM data). DD31–DD00 also output status<br>information to indicate buffer operation type and port number. Internal pullup resistors are provided.<br>DD31 is the most significant bit and the DD00 is the least significant bit. |

| DRAS                                                                                                                                                                                                                                                                                         | 190                                                                                                                                                                                                                                                      | 0   | None     | SDRAM row address strobe. DRAS, with DCAS and DW, supplies the SDRAM commands.                                                                                                                                                                                                     |

| DW                                                                                                                                                                                                                                                                                           | 191                                                                                                                                                                                                                                                      | 0   | None     | SDRAM write select. DW, with DRAS and DCAS, supplies the SDRAM commands.                                                                                                                                                                                                           |

# **TNETX3270** ThunderSWITCH<sup>™</sup> 24/3 ETHERNET<sup>™</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B - NOVEMBER 1997 - REVISED APRIL 1999

## **Terminal Functions (Continued)**

## host DIO interface

| TERMIN<br>NAME                                                               | IAL<br>NO.                                           | I/O | INTERNAL<br>RESISTOR | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------|------------------------------------------------------|-----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAD1<br>SAD0                                                                 | 143<br>142                                           | I   | Pullup               | DIO address bus. SAD1 and SAD0 select the internal host registers, when SDMA is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SCS                                                                          | 138                                                  | Ι   | Pullup               | DIO chip select. When low, SCS indicates a DIO port access is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDMA                                                                         | 123                                                  | I   | Pullup               | DIO DMA select. When low, SDMA modifies the behavior of the DIO interface to allow it to operate<br>with an external DMA controller. The SAD0 and SAD1 terminals are not used to select the internal<br>host register for the access. Instead, the DIO address to access is provided by the DMA address<br>register, and one of two host register addresses is selected according to DMAinc in the Syscontrol<br>register.<br>– If DMAinc = 1, accesses are the DIOdatainc register and DMAaddress increments after each<br>access.<br>– If DMAinc = 0, accesses are the DIOdata register, and DMAaddress does not increment after<br>each address. |

| SDATA7<br>SDATA6<br>SDATA5<br>SDATA4<br>SDATA3<br>SDATA2<br>SDATA1<br>SDATA0 | 136<br>135<br>133<br>131<br>130<br>129<br>127<br>126 | I/O | Pullup               | DIO data interface bus (byte-wide bidirectional DIO port). SDATA7 is the most significant bit and SDATA0 is the least significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SINT                                                                         | 140                                                  | 0   | None                 | DIO interrupt line (interrupt to the attached microprocessor). The interrupt originating event is stored in the Int register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                              |                                                      |     |                      | DIO ready signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SRDY                                                                         | 139                                                  | 0   | Pullup               | <ul> <li>When low during reads, <u>SRDY</u> indicates to the host when data is valid to be read.</li> <li>When low during writes, <u>SRDY</u> indicates when data has been received after SCS is taken<br/>high. <u>SRDY</u> is driven high for one clock cycle before placing the output in high impedance.</li> </ul>                                                                                                                                                                                                                                                                                                                             |

|                                                                              |                                                      |     |                      | DIO read not write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SRNW                                                                         | 125                                                  | Ι   | Pullup               | <ul> <li>When high, read operation is selected.</li> <li>When low, write operation is selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SRXRDY                                                                       | 145                                                  | 0   | None                 | Network management port, receive ready. When high, SRXRDY indicates that the network management port's RX buffers are empty and the network management port is able to receive a frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| STXRDY                                                                       | 144                                                  | 0   | None                 | <ul> <li>Network management port, transmit ready. STXRDY indicates that at least one frame buffer is available to be read by the management CPU.</li> <li>It outputs as a 1 if any of the end-of-frame (EOF) bits, start-of-frame (SOF) bits, or one of the bits in NMTxcontrol is set to 1.</li> <li>Otherwise, it outputs 0.</li> </ul>                                                                                                                                                                                                                                                                                                           |

## TNETX3270 ThunderSWITCH<sup>TM</sup> 24/3 ETHERNET<sup>TM</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B - NOVEMBER 1997 - REVISED APRIL 1999

## **Terminal Functions (Continued)**

| TERMIN<br>NAME | IAL<br>NO. | I/O      | INTERNAL<br>RESISTOR | DESCRIPTION                                                                                                                                                                                                                     |

|----------------|------------|----------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDCLK          | 121        | O/High Z | Pullup               | Serial MII management data clock. MDCLK can be disabled (high impedance) through the use of the SIO register.                                                                                                                   |

| MDIO           | 120        | I/O      | Pullup               | Serial MII management data I/O. MDIO can be disabled, placed in high Z, through the SIO register. An external 4.7-k $\Omega$ pullup resistor, conected to V <sub>DD(3.3V)</sub> , is needed to meet the rise-time requirements. |

| MRESET         | 119        | O/High Z | Pullup               | Serial MII management reset. MRESET can be disabled (high impedance) through the use of the SIO register. If connected to a PHY device, an external pullup resistor is recommended.                                             |

## serial MII management PHY interface

## **EEPROM** interface

| TERMI<br>NAME | NAL<br>NO. | I/O INTERNAL RESISTOR |        | DESCRIPTION                                                                                                                                                                                                                                 |

|---------------|------------|-----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

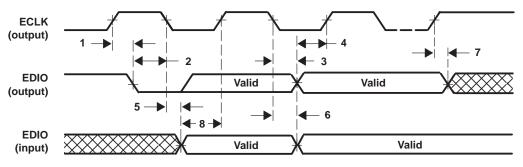

| ECLK          | 117        | 0                     | None   | EEPROM data clock.                                                                                                                                                                                                                          |

| EDIO          | 116        | I/O                   | Pullup | EEPROM data I/O. An external pulldown resistor may be required for proper operation. Since this terminal has an internal pullup, it can be left unconnected if no EEPROM is present. The EEPROM is optional if a management CPU is present. |

## LED interface

| TERMIN  | AL  | I/O | INTERNAL | DESCRIPTION                                                                                                                                                                                   |

|---------|-----|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. |     | RESISTOR | DESCRIPTION                                                                                                                                                                                   |

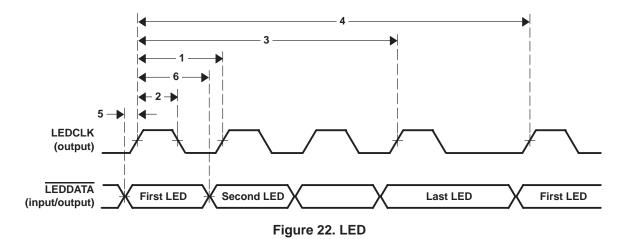

| LEDCLK  | 113 | 0   | None     | LED clock (serial shift clock for the LED status data)                                                                                                                                        |

| LEDDATA | 114 | 0   | None     | LED data (serial LED status data). LEDDATA is active low. All LED information (port link, activity status, software status, flow status, and fault status) is sent via this serial interface. |

## **JTAG** interface

| TERMI | NAL | 1/0 | INTERNAL DESCRIPTION | DESCRIPTION                                                                                                                                                                                                                                                                   |  |

|-------|-----|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME  | NO. | 1/0 | RESISTOR             | DESCRIPTION                                                                                                                                                                                                                                                                   |  |

| TCLK  | 106 | I   | Pullup               | Test clock. TCLK is used to clock state information, test instructions, and test data into and out of the device during operation of the test port.                                                                                                                           |  |

| TDI   | 110 | I   | Pullup               | Test data input. TDI is used to serially shift test data and test instructions into the device during operation of the test port. An internal pullup resistor is provided on TDI to ensure JTAG compliance.                                                                   |  |

| TDO   | 108 | 0   | None                 | Test data output. TDO is used to serially shift test data and test instructions out of the device during operation of the test port.                                                                                                                                          |  |

| TRST  | 111 | I   | Pullup               | Test reset. TRST is used for asynchronous reset of the test-port controller. An internal pullup resistor is provided to ensure JTAG compliance. If the test port is not used, an external pulldown resistor of 10 k $\Omega$ may be used to disable the test-port controller. |  |

| TMS   | 107 | I   | Pullup               | Test mode select. TMS is used to control the state of the test-port controller. An internal pullup resistor is provided on TMS to ensure JTAG compliance.                                                                                                                     |  |

# **TNETX3270** ThunderSWITCH<sup>™</sup> 24/3 ETHERNET<sup>™</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B - NOVEMBER 1997 - REVISED APRIL 1999

## **Terminal Functions (Continued)**

## miscellaneous

| TERMI | NAL | 1/0 | INTERNAL | DESCRIPTION                                                                                    |  |

|-------|-----|-----|----------|------------------------------------------------------------------------------------------------|--|

| NAME  | NO. | 1/0 | RESISTOR |                                                                                                |  |

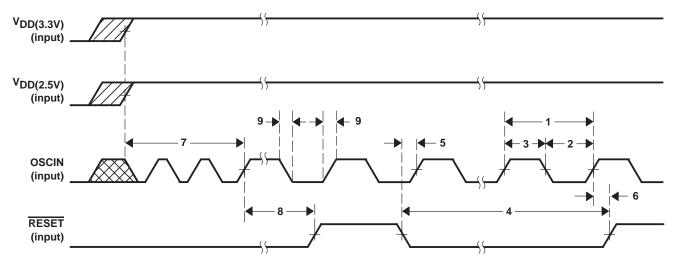

| OSCIN | 112 | Ι   | None     | Master system clock input (83.33-MHz input clock)                                              |  |

| RESET | 115 | Ι   | None     | Reset. RESET is synchronous and, therefore, the system clock must be operational during reset. |  |

#### power interface

|                       | TERMINAL                                                                                                               | INTERNAL | DESCRIPTION                                                                           |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------|

| NAME                  | NO.                                                                                                                    | RESISTOR | DESCRIPTION                                                                           |

| GND                   | 8, 14, 34, 40, 55, 68, 74, 81, 88, 94, 100,<br>128, 134, 141, 148, 154, 160, 175, 188,<br>194, 201, 208, 214, 220, 235 | None     | Ground. GND is the 0-V reference for the device. All GND terminals must be connected. |

| V <sub>DD(3.3V)</sub> | 12, 72, 109, 122, 132, 163, 169, 192, 229                                                                              | None     | 3.3-V supply voltage. Power for the input, output, and I/O terminals.                 |

| V <sub>DD(2.5V)</sub> | 4, 17, 31, 45, 58, 64, 77, 91,<br>105, 118, 124, 137, 151, 165, 178,<br>184, 197, 211, 225, 238                        | None     | 2.5-V supply voltage. Power for the core.                                             |

## summary of signal terminals by signal group function

| PORT DESCRIPTION      | NUMBER OF<br>SIGNALS | MULTIPLIER | TOTAL |  |  |

|-----------------------|----------------------|------------|-------|--|--|

| LED                   | 2                    | 1          | 2     |  |  |

| 10-Mbit/s port        | 16                   | 3          | 48    |  |  |

| 10-/100-Mbit/s port   | 19                   | 3          | 57    |  |  |

| DIO                   | 17                   | 1          | 17    |  |  |

| EEPROM interface      | 2                    | 1          | 2     |  |  |

| DRAM interface        | 50                   | 1          | 50    |  |  |

| Miscellaneous         | 2                    | 1          | 2     |  |  |

| JTAG                  | 5                    | 1          | 5     |  |  |

| Serial MII management | 3                    | 1          | 3     |  |  |

| Total signals         |                      |            |       |  |  |

|                       | SUMMARY              |            |       |  |  |

| Assigned terminals    |                      |            | 186   |  |  |

| V <sub>DD(3.3V)</sub> | 9                    |            |       |  |  |

| V <sub>DD(2.5V)</sub> | 20                   |            |       |  |  |

| GND                   | 25                   |            |       |  |  |

| Total terminals       |                      |            | 240   |  |  |

## **DIO register groups**

| REGISTERS             | LOADABLE<br>USING 24C02<br>EEPROM? | LOADABLE<br>USING 24C08<br>EEPROM? | DIO<br>ADDRESS<br>RANGE |

|-----------------------|------------------------------------|------------------------------------|-------------------------|

| Port configuration    | Yes                                | Yes                                | 0x0000:0x002F           |

| Spanning tree         | Yes                                | Yes                                | 0x0030:0x007F           |

| Trunking              | Yes                                | Yes                                | 0x0080:0x0088           |

| VLAN                  | No                                 | Yes                                | 0x0089:0x03FF           |

| Port status           | No                                 | No                                 | 0x0400:0x043F           |

| Address configuration | No                                 | No                                 | 0x0440:0x08FF           |

| Port statistics       | No                                 | No                                 | 0x0900:0xFFFF           |

### Table 1. Internal Register and Statistics Memory Map

# **TNETX3270** ThunderSWITCH<sup>™</sup> 24/3 ETHERNET<sup>™</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B - NOVEMBER 1997 - REVISED APRIL 1999

#### Table 2. Detailed DIO Register Map

| BYTE 3    | BYTE 2            | BYTE 1          | BYTE 0       | DIO<br>ADDRESS |  |  |  |

|-----------|-------------------|-----------------|--------------|----------------|--|--|--|

| Port1c    | control           | Port0c          | ontrol       | 0x0000         |  |  |  |

| Port3c    | control           | Port2c          | Port2control |                |  |  |  |

| Port5c    | control           | Port4c          | ontrol       | 0x0008         |  |  |  |

| Port7c    | control           | Port6c          | ontrol       | 0x000C         |  |  |  |

| Port9c    | control           | Port8c          | ontrol       | 0x0010         |  |  |  |

| Port11    | control           | Port10          | control      | 0x0014         |  |  |  |

| Port13    | control           | Port120         | control      | 0x0018         |  |  |  |

| Port15    | control           | Port14          | control      | 0x001C         |  |  |  |

| Port17    | control           | Port160         | control      | 0x0020         |  |  |  |

| Port19    | control           | Port180         | control      | 0x0024         |  |  |  |

| Port21    | control           | Port200         | control      | 0x0028         |  |  |  |

| Port23    | control           | Port220         | control      | 0x002C         |  |  |  |

| Port25    | control           | Port240         | control      | 0x0030         |  |  |  |

| Rese      | erved             | Port260         | control      | 0x0034         |  |  |  |

| Rese      | erved             | Rese            | rved         | 0x0038:0x003F  |  |  |  |

| Reserved  | UnkVLANport       | Mirrorport      | Uplinkport   | 0x0040         |  |  |  |

| Rese      | erved             | Aging threshold |              | 0x0044         |  |  |  |

|           | Rese              | erved           |              | 0x0048:0x004F  |  |  |  |

|           | Nlearnports       |                 |              |                |  |  |  |

|           | 0x0054            |                 |              |                |  |  |  |

|           | Rxuniblockports   |                 |              |                |  |  |  |

|           | Rxmultiblockports |                 |              |                |  |  |  |

|           | Unkur             | niports         |              | 0x0060         |  |  |  |

|           | Unkmu             | ltiports        |              | 0x0064         |  |  |  |

|           | Unksr             | cports          |              | 0x0068         |  |  |  |

|           | UnkVLAI           | Nintports       |              | 0x006C         |  |  |  |

|           | Rese              | erved           |              | 0x0070:0x007F  |  |  |  |

| Trunkmap3 | Trunkmap2         | Trunkmap1       | Trunkmap0    | 0x0080         |  |  |  |

| Trunkmap7 | Trunkmap6         | Trunkmap5       | Trunkmap4    | 0x0084         |  |  |  |

|           | Reserved          |                 | Trunkports   | 0x0088         |  |  |  |

|           | Rese              | erved           |              | 0x008C:0x009F  |  |  |  |

| Devcode   | Reserved          | SIO             | Revision     | 0x00A0         |  |  |  |

|           | Rese              | erved           |              | 0x00A4:0x00DF  |  |  |  |

| RAMsize   | Reserved          | IOBco           | ontrol       | 0x00E0         |  |  |  |

|           | Rese              | erved           |              | 0x00E4         |  |  |  |

| Pauseti   | ime100            | Pauset          | ime10        | 0x00E8         |  |  |  |

|           | Rese              | erved           |              | 0x00EC         |  |  |  |

| Reserved  |                   | Flowthreshold   |              | 0x00F0         |  |  |  |

| Rese      | erved             | LEDcontrol      |              | 0x00F4         |  |  |  |

| Sysco     | ontrol            | Statcontrol     |              | 0x00F8         |  |  |  |

# **TNETX3270** ThunderSWITCH<sup>TM</sup> 24/3 ETHERNET<sup>TM</sup> SWITCH WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

## Table 2. Detailed DIO Register Map (Continued)

| BYTE 3 | BYTE 2                     | BYTE 1        | BYTE 0 | DIO<br>ADDRESS |  |  |  |

|--------|----------------------------|---------------|--------|----------------|--|--|--|

|        | Reserved (for              | r EEPROM CRC) |        | 0x00FC         |  |  |  |

|        | 0x0100                     |               |        |                |  |  |  |

|        | 0x0104                     |               |        |                |  |  |  |

|        | VLA                        | N2ports       |        | 0x0108         |  |  |  |

|        | VLA                        | N3ports       |        | 0x010C         |  |  |  |

|        | VLA                        | N4ports       |        | 0x0110         |  |  |  |

|        | VLA                        | N5ports       |        | 0x0114         |  |  |  |

|        | VLA                        | N6ports       |        | 0x0118         |  |  |  |

|        | VLA                        | N7ports       |        | 0x011C         |  |  |  |

|        | VLA                        | N8ports       |        | 0x0120         |  |  |  |

|        | VLA                        | N9ports       |        | 0x0124         |  |  |  |

|        | VLAN                       | N10ports      |        | 0x0128         |  |  |  |

|        | VLA                        | N11ports      |        | 0x012C         |  |  |  |

|        | VLA                        | N12ports      |        | 0x0130         |  |  |  |

|        | VLAN                       | N13ports      |        | 0x0134         |  |  |  |

|        | VLAN                       | N14ports      |        | 0x0138         |  |  |  |

|        | VLAN                       | N15ports      |        | 0x013C         |  |  |  |

|        | VLAN                       | N16ports      |        | 0x0140         |  |  |  |

|        | VLAN                       | N17ports      |        | 0x0144         |  |  |  |

|        | VLAN18ports                |               |        |                |  |  |  |

|        | 0x014C                     |               |        |                |  |  |  |

|        | 0x0150                     |               |        |                |  |  |  |

|        | 0x0154                     |               |        |                |  |  |  |

|        | 0x0158                     |               |        |                |  |  |  |

|        | VLAN22ports<br>VLAN23ports |               |        |                |  |  |  |

|        | 0x0160                     |               |        |                |  |  |  |

|        | VLAN                       | N25ports      |        | 0x0164         |  |  |  |

|        | VLA                        | N26ports      |        | 0x0168         |  |  |  |

|        | VLAN                       | N27ports      |        | 0x016C         |  |  |  |